半导体测试

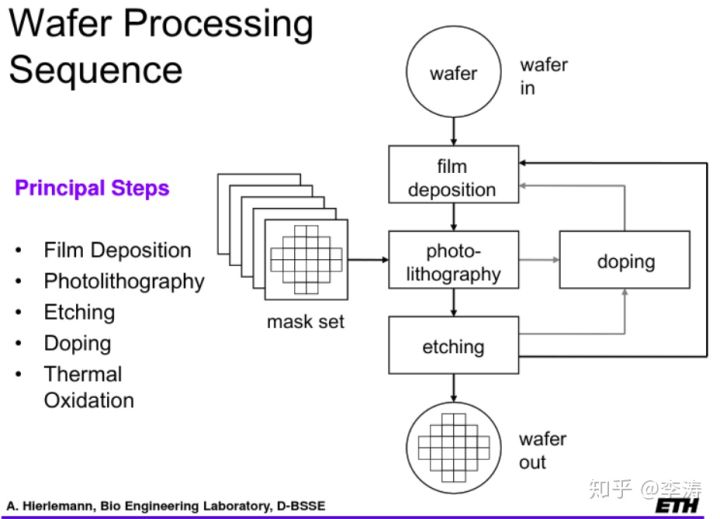

以wafer的工艺流程为例,从mask set到真正的wafer,需要经过很多复杂的加工步骤。每个加工步骤可以抽象成 zi=Fi(xi,yi) 。 xi 是输入, yi 是该加工的process variant, zi是输出。因为每个加工步骤 yi的存在,最终得到的wafer上的芯片会一定概率的存在故障点,或者某些门以及走线的某些参数严重偏离设计要求,这些都会导致芯片功能问题。

半导体测试是什么?

传统意义的半导体测试指基于ATE机台的产品测试,分为wafer level的CP测试(chip probing)或FE测试(FrontEnd test)和封装之后的FT测试(final test)或BE测试(backend test)。当然随着WLCSP (wafer level chip scale package)封装的推广,越来越多产品只需要CP测试后就可以切割分片供货了。

传统的半导体测试是高度依赖DFT设计,完备的DFT设计可以提供高故障覆盖率的测试激励,保证半导体测试可以用最小的时间成本筛选出有故障的芯片。但是随着芯片软硬件复杂度的提高,许多问题无法或很难抽象出相应的故障模型,因此SLT(system level test)也被多数公司采用,放在FT测试之后整个FT测试的故障覆盖率,保证DPM(defects per million )满足客户需求。

为什么半导体测试是必须的?

芯片在设计阶段有完备的验证流程,仿真验证、UVM、形式验证以及基于FPGA的SLE(system level emulation)等等验证手段可以保证100%设计功能正确性。一般来说芯片可以流片,芯片的netlist是通过验证的所有测试用例,完美实现设计需求的。 因此很多人会奇怪为什么每一个芯片都需要费时费力的经过严格的半导体测试,才能提供给客户呢?

以wafer的工艺流程为例,从mask set到真正的wafer,需要经过很多复杂的加工步骤。每个加工步骤可以抽象成 zi=Fi(xi,yi) 。 xi 是输入, yi 是该加工的process variant, zi是输出。因为每个加工步骤 yi的存在,最终得到的wafer上的芯片会一定概率的存在故障点,或者某些门以及走线的某些参数严重偏离设计要求,这些都会导致芯片功能问题。

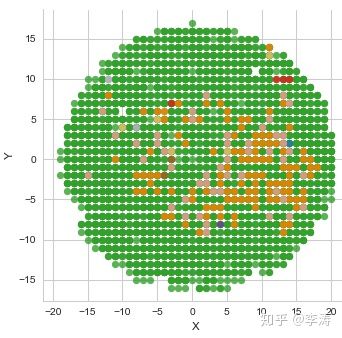

以成熟的28nm工艺为例,总体yield在93%左右(wafer的yield一般在93%左右而封装后的yield一般在99%)。一个复杂电子产品比如手机需要集成很多芯片在一个基板上,整个系统的DPM是每个芯片的DPM乘积,因此每个芯片的DPM 需要控制在500以下以保证集成商可以低成本的生产出合格可靠的电子产品。为了达到DPM的目标,半导体测试是保证芯片出厂品质所不能缺少的一步。而随着半导体工艺的不断下探1nm,量产工艺的总体yield也下降到80%左右,更多的产品生产故障率进一步要求更完备的半导体测试,否则低故障覆盖率的测试会导致大量customer return,影响产品的量产上市时间。

半导体测试的数据结果也用于工艺监控和优化以及产品设计优化中。比如scan/mbist测试一般会将故障的具体信息存储在数据库,大量产品测试的这些故障信息会反标到wafer具体die上,甚至反标到layout的X/Y坐标上,如果有明显的defect signature出现,工艺和设计就需要检查是否有什么原因造成这种通用问题, 是否有可以改进的地方。

半导体测试也用stress加速老化测试,减少或者避免burn-in。burn-in一般需要125C/24h,目的是根据澡盆曲线,将早期失效的DUT通过stress筛选出来。因为burn-in的时间一般很长,多数产品在ATE测试中加入超高电压短时stress测试可以加速老化,用最短的stress时间快速筛选出早期失效的DUT。

芯片根据应用领域不同,Jedec(Home | JEDEC)会有不同的qualification的要求,一般qualification包括ESD/latchup,HTOL,TC,ELFR,HTS,THB等等。无论哪种qualification,在stress之前要使用完备的ATE测试程序筛选出完好的芯片,在stress之后需要使用相同的程序做readout,判断芯片是否经过stress后损坏。因此对于qualification而言ATE测试也是不可或缺的,需要在项目中和测试工程师合作制定可行的计划。

半导体测试流程

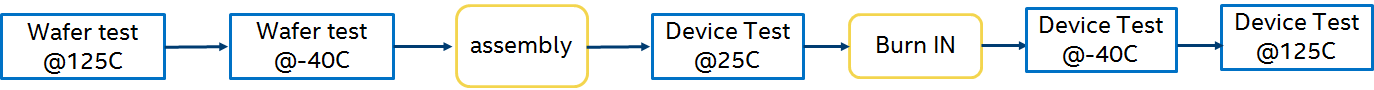

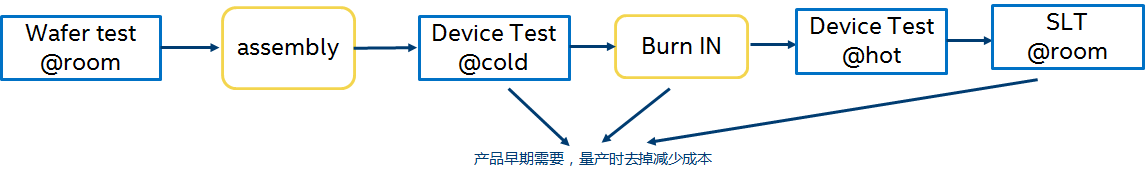

芯片根据应用领域,温度和可靠性要求的不同,需要定义不同的test insertion。比如汽车电子的产品测试流程如下共有5个test insertion,如此多的test insertion是因为汽车电子的DPM要求zero defect,必须在不同温度下多次测试最大限度地筛选新品。

而一般用于消费类比如手机通讯的芯片,因为不涉及生命和公共安全,DPM要求一般在500附近,因此测试的流程也尽可能的简化去降低测试成本。如下图所示,根据工艺在不同温度对logic/sram的影响,决定wafer和device的测试温度。

因为增加一个test insertion,测试成本就会显著增加,产品利润就会降低。因此半导体测试的一个重要工作是研究如何用尽量少的test insertion达到同样的DPM目标。以上图为例,在项目的早期定下目标是“量产程序需要去除device test@cold,burn-in以及SLT”,在早期测试程序开发过程中,就需要研究尝试如何在保留的test insertion中增加更多的测试(比如scan/mbist/IO stress测试,更严格的pass/fail limit等等),以达到筛选出同样有问题的芯片。

如何定义不同test insertion的测试内容呢? 概括而言是需要测试工程师根据故障概率,测试时间和测试条件的综合评估而定。

wafer test使用探针卡+probe实现芯片与ATE机台的电气连接,一般而言探针卡的接触电阻以及感性阻值较大,尽量避免测试频率高的测试(限制在50M~100M以内),而将重点放在scan/mbist等故障率比较高的测试上,保证90%以上的defect可以在wafer level筛出而不浪费assembly和FT测试的cost。

FT测试一般在早期需要实现所有的测试以保证测试覆盖率。除了筛选defect之外,一般FT测试还需trim一些analog模块比如bandgap,reference current,reference resistance等等,以及其他一些需要将结果写到fuse内的测试。

SLT一般使用类似系统应用板搭建的mini-system执行系统应用软件,筛选出无法用DFT的故障模型表征的defect,或者是ATE机台受限的一些和性能相关的功能测试。但是因为SLT测试不容易提供工艺和设计改进需要的具体数据,一般需要在量产过程中提高ATE测试的故障覆盖率以及有效性,最大限度地减少进入SLT测试的defect device的数量,最终目标是去除SLT测试。